Materials have emerged as a growing challenge across the semiconductor supply chain, as chips continue to scale, or as they are utilized in new devices such as sensors for AI or machine learning systems.

Engineered materials are no longer optional at advanced nodes. They are now a requirement, and the amount of new material content in chips continues to grow along with density and increased functionality. This is obvious at 5nm and beyond, but the trend toward solving issues with materials is occurring in markets where not everything is being created at the latest process nodes. The need for longevity in safety-critical markets such as automotive, medical and avionics, as well as in industrial applications, has brought materials science to the forefront of the semiconductor industry.

“One of the misconceptions in AI is that it’s all about the algorithms for training and inferencing,” said Dominic Miranda, business development manager at Brewer Science. “But the input of the data coming into those systems is equally important. There are multiple sensors in networks, factories and municipalities, and there is a vast volume of data. So the speed of the data is important, and so is the speed of the sensors to react to a variety of data. Materials have a big impact on the speed of the sensor to react to stimuli.”

There is research currently underway, for example, in carbon-based technology using carbon nanotubes or graphene as an active layer.

“The way you functionalize these devices with materials affects how a sensor behaves or what it can sense,” Miranda said. “The more complex the device, the more you have to deal with noise. That can be environmental noise, like the acoustic noise from machines running or vibration. What we’re finding is that the market is going in two directions. You can take sensors off the shelf and apply them to a system, or you can use a custom-design to get a cleaner signal.”

Noise is a growing problem, particularly at advanced nodes where tolerances are much tighter than at older nodes. While this used to be a challenge primarily for analog circuitry in proximity of digital switching, thinner gate oxides and increased density at 10/7nm and below have made noise from power, electromagnetic interference, and heat an increasingly thorny issue even in digital circuits.

The march to 2D

One of the challenges in shrinking devices is that silicon, like most materials, is inherently three-dimensional. Even if a silicon layer is only one atom thick, it still includes dangling bonds that extend out of the plane of the surface. These bonds require passivation to avoid undesirable interactions, and introduce surface roughness that causes carrier scattering and degrades mobility.

In contrast, there are no out-of-plane bonds in two-dimensional semiconductors. A single atomic layer is structurally “complete” and self-passivating, reducing or eliminating short-channel effects.

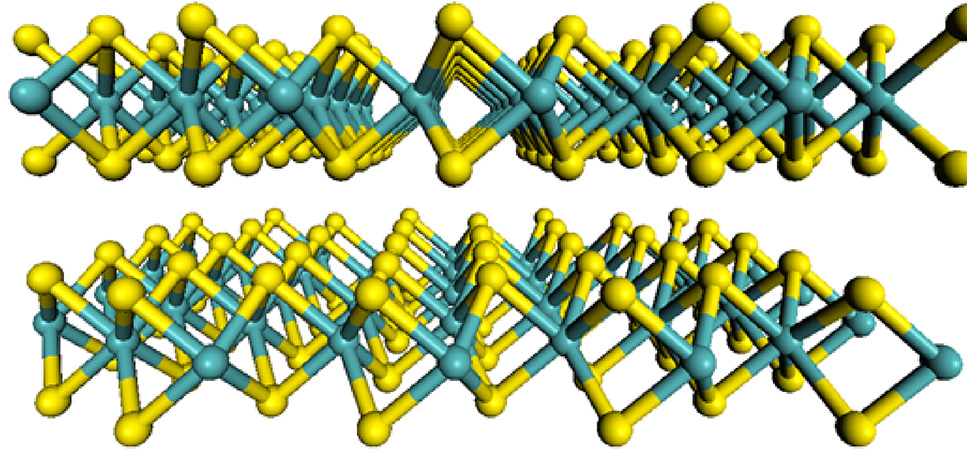

Exploiting these promising structural properties in manufacturable devices has been challenging, though. Graphene, the first 2D semiconductor discovered, has no band gap. Black phosphorus is unstable at typical operating temperatures. Instead, much current research focuses on transition metal dichalcogenides like MoS2, WS2, and WSe2. Several papers at both the Materials Research Society Spring Meeting in April and last December’s IEEE Electron Device Meeting examined the physics and materials science of these compounds.

Simply fabricating 2D materials is the first challenge for commercial applications. Abundant research samples can be obtained by exfoliation — graphene was isolated by using sticky tape to pull layers off of bulk graphite — but the precision and quality requirements of manufacturing demand a more controllable method.

While CVD is an obvious choice for thin layer deposition, CVD of 2D materials is more complex than it might appear at first glance. For example, a 2D material may rest on a substrate, but is not bonded to it. Thus, growing a 2D semiconductor typically involves etching or ablating the nucleation layer out from underneath the semiconducting monolayer in order to isolate it. Xiangfeng Duan, professor of chemistry and biochemistry at UCLA, explained in an MRS presentation that the multilayer stacks needed for devices require careful attention to chemical compatibility with the substrate, between the components of the stack, and between process gases. Process conditions that are ideal for one layer can cause chemical or thermal degradation of the next layer.

When 2D semiconductor heterostructures are successfully deposited, though, the results can be dramatic. Duan’s group made atomically thin lateral WSe2/WS2 p-n diodes, with the two materials interacting along a single quantum line. For vertical stacks, they are investigating intercalation of electrically passive materials into existing stacks. This approach can potentially isolate monolayers from each other without the added complexity of substrate removal.

Simple isolation of individual layers is not enough, though. In a 2D material, defects can prevent the movement of carriers altogether: they can’t leave the plane to find an alternative path. Reporting on his optoelectronic device research, Ali Javey, professor of electrical engineering and computer science at UC Berkeley, observed that defects are non-radiative recombination centers. As a result, quantum yield gives a reasonable measure of defect levels.

Once high quality semiconductor material is achieved, low-resistance contacts are the next challenge. A contact with good electron mobility may impede holes, and vice versa. Javey’s group demonstrated optoelectronic emitters by using alternating current to supply first holes, then electrons, which recombined in exfoliated MoS2 layers to emit light. In grown, rather than exfoliated materials, the substrate’s coefficient of thermal expansion can be used to control the amount of strain in the deposited film, shifting the band gap and emission characteristics.

In work presented at IEDM, Ph.D. student Xuejun Xie and colleagues at UC Santa Barbara described the use of light-sensitive MoS2 FETs in an artificial retina device. Such a device is potentially useful for neuromorphic image recognition applications. While memristive crossbar arrays are frequently proposed for use as artificial synapses, they cannot “see” an image directly.

Capturing image information and writing it to the crossbar array is a potentially significant bottleneck that might be alleviated by combining image sensing and analysis in a single device. To this end, the Santa Barbara group created an array of metallic MoS2 quantum dots on the semiconducting MoS2 channel using e-beam patterning. The quantum dots attract abundant electrons from the conduction band of the semiconductor, moving the Fermi level toward the valence band. Holes are trapped, increasing resistance. As current flows, mobile electrons recombine with the holes, causing resistance decay over time. There are more carriers where the light is on, so the device “detects” and “remembers” bright parts of the image.

Even 14 years after the discovery of graphene, devices based on 2D semiconductors are still in their infancy.

Flexible materials

Part of the challenge in materials engineering these days is to reach beyond standard formats for chips. There is a whole new wave of flexible hybrid electronics that includes everything from thin-film temperature sensors to electronic ink, each with its own unique properties and challenges. And they are making it much more difficult to ensure that these materials will work as planned under a range of new and sometimes unexpected operating conditions.

“There is a range of sensors for glucose, pH, humidity and temperature, said Norman Chang, chief technologist for the semiconductor business unit at ANSYS. “The problem is that we are exercising components with different thermal gradient solutions, which can have an impact on performance. You’re really looking at a 3D geometry input, and that requires co-simulation of the flexible substrate and the package because they can impact the electrical performance of these devices. It all has to be simulated together. If you look at printed RF, millimeter wave performance may be different in different areas.”

One of the new approaches being developed is called geometry wrapping, whereby circuits can literally be wrapped around any device or even stretched across buildings. The U.S. Air Force Research Laboratory, for example, announced earlier this year that it is developing a flexible circuit system in conjunction with NextFlex for IoT sensor applications for military and commercial applications. The goal is to achieve stretchable electronics that can withstand extremely high G forces and temperatures.

Flexible sensors are also being used for such applications as water and environmental testing. “With water testing, the challenge is to design a sensor to ignore everything but what you want to test for,” said Brewer’s Miranda. “This doesn’t work well with solid-state materials, but it does work with flexible sensors. You’ve probably heard the video on YouTube where some people hear Yanni and others hear Laurel, depending upon the wavelength they’re hearing. But materials can be used to make sure that you hear what you’re supposed to hear, and they can be used to detect only what you want to detect.”

Conclusion

The emphasis on materials engineering in electronics is growing, and it will continue to become more pervasive. While device scaling is an obvious place for new materials, there are a bunch of new markets such as autonomous driving, AI, 5G, and industrial and medical applications where electronics have played a much more limited role in the past.

Not all of those will use conventional chips, and many have specific requirements for flexibility, noise sensitivity and signal throughput.

Your site has excellent material. I bookmarked the site

Have you ever had issues with your web host?

I’m open for recommendations as my webhost is dreadful now.

I discovered your website from Google and also I

need to claim it was a great find. Thanks!